Лекция 9. Структура процессора

1

Структура процессора станет совершенно понятной, если задуматься над тем, какие операции ему предстоит выполнять при обработке машинной команды.

• Извлечение команды — процессор считывает команду из памяти.

• Интерпретация команды — процессор расшифровывает команду и определяет, какие операции ему предстоит выполнить.

• Извлечение данных — для выполнения команды может потребоваться прочесть данные из памяти или из модуля ввода-вывода.

• Обработка данных — выполнение команды может потребовать преобразования данных, т.е. выполнения над ними определенных арифметических или логических операций.

• Запись данных

Чтобы выполнить перечисленные операции, процессору требуются определенные средства временного хранения информации. Ему нужно помнить, где находится выполняемая команда, и тогда можно будет определить, откуда выбрать следующую. Ему нужно хранить коды команд и данных во время их обработки. Другими словами, процессор нуждается в собственной внутренней памяти.

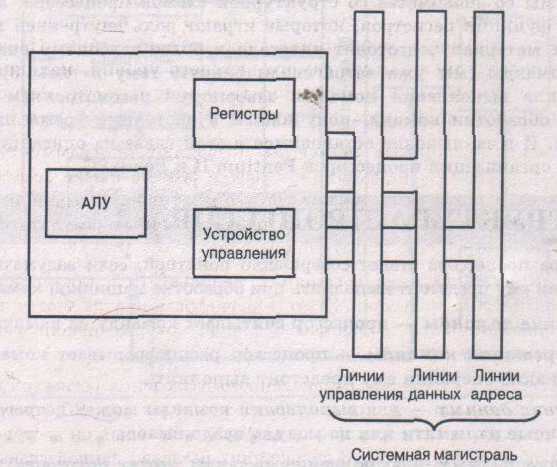

На рис. 11.1 представлена упрощенная структурная схема процессора, на которой видно, как он взаимодействует с остальными компонентами компьютера через системную магистраль. Аналогичный интерфейс, как было описано в главе 3, должны иметь все взаимодействующие компоненты компьютера. Читатель должен припомнить, что главными структурными компонентами процессора являются арифме тическое и логическое устройство (АЛУ) и устройство (или узел) управления (УУ). На АЛУ возлагаются собственно вычисления, т.е. преобразование информации, а УУ управляет как потоком данных и команд, поступающих в процессор и выходящих из него, так и порядком выполнения операций в АЛУ. Кроме того, на этой схеме показана и внутренняя память процессора — набор регистров.

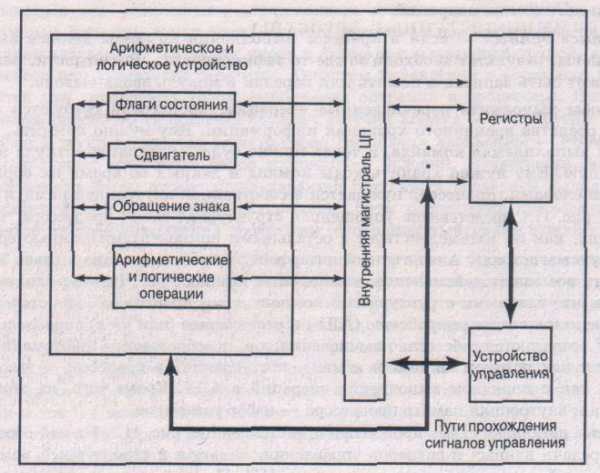

Более детальная схема процессора представлена на рис. 11.2. На ней обозначены пути передачи данных и сигналов управления, включая и структурный компонент, обозначенный как внутренняя магистраль ЦП. По этой магистрали данные передаются между регистрами и АЛУ, поскольку АЛУ может оперировать только с данными, хранящимися в регистрах. На этой же схеме показана и типовая структура АЛУ. Обратите внимание на определенную схожесть структуры компьютера в целом и одного из его компонентов — центрального процессора. В обеих схемах несколько основных компонентов связываются между собой через магистраль.

Рис. 11.1. Укрупненная структурная схема процессора

Рис. 11.2, Внутренняя структура процессора

Организация набора регистров

Память в компьютерной системе имеет иерархическую структуру. Чем более высокое положение в иерархии занимает определенный блок памяти, тем выше его быстродействие, меньше объем и выше стоимость хранения в пересчете на 1 бит. Набор регистров процессора представляет память самого верхнего уровня, находящегося в иерархии над уровнями оперативной памяти и кэш-памяти. Регистры процессора разделяются по функциям.

• Программно доступные регистры позволяют программисту, разрабатывающему программы на машинном языке или на языке ассемблера, минимизировать в программе обращение к оперативной памяти и, где это возможно, использовать для хранения промежуточных результатов быстродействующую внутреннюю память процессора.

• Регистры управления и состояния используются для управления функционированием процессора. К этим регистрам иногда могут иметь доступ специальные привилегированные команды, которые используются только в программах операционной системы.

Не существует раз и навсегда узаконенного разделения регистров на эти категории. Например, в большинстве компьютеров счетчик команд, PC, программно недоступен, но существуют и такие машины, как VAX, в которых он доступен со стороны программы, как и любой другой. В дальнейших разделах данной главы мы все-таки будем опираться на разделение регистров на эти две категории.

3. Функциональная и структурная организация центрального процессора эвм

В области вычислительной техники различают процессоры центральные, специализированные, ввода-вывода, передачи данных и коммуникационные.

3.1. Назначение и структура центрального процессора

Центральный процессор— основное устройство ЭВМ, которое наряду с обработкой данных выполняет функции управления системой: инициирование ввода-вывода, обработку системных событий, управление доступом к основной памяти и т.п.

Организация центрального процессора (ЦП) определяется архитектурой и принципами работы ЭВМ (состав и форматы команд, представление чисел, способы адресации, общая организация машины и её основные элементы), а также технико-экономическими показателями.

Логическую структуру ЦП представляет ряд функциональных средств (рис. 3.1): средства обработки, средства управления системой и программой, локальная память, средства управления вводом-выводом и памятью, системные средства.

Средства обработки обеспечивают выполнение операций с фиксированной и плавающей точкой, операций с десятичными данными и полями переменной длины. Локальная память состоит из регистров общего назначения и с плавающей точкой, а также управляющих регистров. К средствам управления памятью относятся средства управления доступом к ОП и предвыборкой команд, буферная память, средства защиты памяти. Средства управления вводом-выводом обеспечивают приоритетный доступ программ через контроллеры (каналы) к периферийному оборудованию. К системным средствам относятся средства службы времени: часы астрономического времени, таймер, коммутатор и т.д.

Существует обязательный (стандартный) минимальный набор функциональных средств для каждого типа центрального процессора. Он включает в себя: регистры общего назначения, средства выполнения стандартного набора операций и средства управления вычислительным процессом. Конкретная реализация ЦП может различаться составом средств, способом их реализации, техническими параметрами.

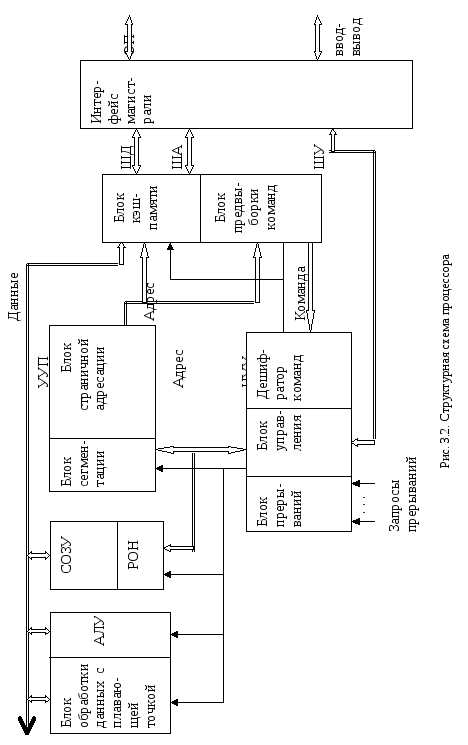

Структурно все функциональные средства разбиваются на следующие устройства (рис. 3.2): центральное устройство управления (ЦУУ), арифметико-логическое устройство (АЛУ), устройство управления памятью (УУП), сверхоперативное запоминающее устройство (СОЗУ), устройство предвыборки команд и данных (УП) и интерфейс магистрали (ИМ).

Центральное устройство управления включает дешифратор команд, блок управления и блок прерываний. Дешифратор команд дешифрирует команды, которые поступают из блока предварительной выборки (очереди команд). Блок управления (БУ) формирует последовательности управляющих сигналов, которые поступают на все блоки процессора, обеспечивающие выполнение очередной команды и переход к следующей. Блок прерываний проводит анализ запросов на прерывания, формирует сигнал прерывания работы процессора и код (вектор) запроса с наивысшим приоритетом.

Арифметико-логическое устройство выполняет все арифметические и логические операции набора команд ЭВМ. В состав устройства входят традиционные арифметико-логические блоки, специализированные аппаратные средства (блок ускоренного умножения), буферные и рабочие регистры, иногда собственный блок управления. Во многих случаях выполнение операций с плавающей точкой осуществляется в отдельном блоке (процессоре), который имеет собственные регистры данных, управления и работает параллельно с центральным процессором.

Сверхоперативное ЗУ (регистровый файл) содержит регистры общего назначения (РОН), в которых хранятся данные и адреса.

Устройство управления памятью (диспетчер памяти) предназначено для сопряжения центрального процессора и подсистемы ввода-вывода с оперативной памятью. Оно состоит из блока сегментации и блока страничной адресации, осуществляющих двухступенчатое формирование физического адреса ячейки памяти: сначала в пределах сегмента, а затем в пределах страницы. Наличие блоков сегментации и страничной адресации, их одновременное функционирование обеспечивают максимальную гибкость проектируемой системы. Сегментация полезна для организации в памяти локальных модулей и является инструментом программиста, в то время как страницы нужны системному программисту для эффективного использования физической памяти системы.

Устройство предвыборки команд и данных включает блок предвыборки команд и внутреннюю кэш-память (кэш-память первого уровня). Первый осуществляет заполнение очереди команд, причем выборка из памяти производится в промежутках между магистральными циклами команд. Внутренняя кэш-память позволяет существенно повысить производительность процессора за счет буферизации в ней часто используемых команд и данных, сокращения числа обращений к оперативной памяти.

Интерфейс магистрали реализует протоколы обмена центрального процессора с памятью, контроллерами (каналами) ввода-вывода, другими активными устройствами системы. Обмен осуществляется с помощью шин данных, адреса и управления. Состав линий управления, тактовая сетка, магистральные циклы обмена существенно отличаются у различных типов процессоров.

В современных суперскалярных процессорах используется целый ряд параллельно функционирующих исполнительных устройств (от 2 до 6 устройств). В их состав могут входить:

несколько целочисленных устройств;

устройство плавающей точки;

устройство выполнения переходов;

устройство загрузки/записи.

Устройство выполнения переходов обрабатывает команды условных переходов. Если условия перехода доступны, то решение о направлении перехода принимается немедленно, в противном случае выполнение последующих команд продолжается по предположению (спекулятивно).

Пересылки данных между кэш-памятью данных, с одной стороны, и регистрами общего назначения и регистрами плавающей точки, с другой стороны, обрабатываются устройством загрузки/записи.

studfiles.net

20. Назначение и основные элементы центрального процессора.

Предыдущий вопрос.

21. Организация и структура памяти.

Память компьютера предназначена для кратковременного и долговременного хранения информации — кодов команд и данных. Информация в памяти хранится в двоичных кодах, каждый бит — элементарная ячейка памяти — может принимать значение «0» или «1». Каждая ячейка памяти имеет свой адрес, однозначно ее идентифицирующий в определенной системе координат. Минимальной адресуемой единицей хранения информации в памяти обычно является байт, состоящий, как правило, из 8 бит.

Со времени появления больших (по размерам) компьютеров деление памяти произошло на внутреннююивнешнюю.

Внутренняя память подразделяется:

— на основную (оперативную), информация в которой может изменяться процессором в любой момент времени;

— постоянную, информацию с которой процессор может только считывать.

Обращение (по чтению или по записи) к ячейкам оперативной памяти может происходить в любом порядке. В связи с этим оперативную память называют памятью с произвольным доступом — Random Access Memory (RAM), в отличие от постоянной памяти (Read Only Memory, ROM).

Внешняя память адресуется более сложным образом — каждая ее ячейка имеет свой адрес внутри некоторого блока, который, в свою очередь, имеет многомерный адрес. Во время физических операций по обмену данными блок может быть считан или записан только полностью.

Для решения задач пользователя ЭВМ должна обладать системой памяти, удовлетворяющей компромиссу ряда критериев:

– максимальный объем, требуемый для решения задачи;

– высокое быстродействие;

– низкая стоимость.

(микропроцессорная память — МПП)

– чем больше объем памяти ЭВМ, тем ниже ее быстродействие и ниже относительная стоимость запоминающих устройств, входящих в систему памяти;

– чем выше быстродействие, тем выше относительная стоимость запоминающих устройств в пересчете на единицу хранимой в памяти информации.

22. Элементы памяти, их назначение, возможности и принцип работы.

Любые ЗУ состоят из элементов (ячеек) памяти (ЭП) – минимальных частей устройства памяти, используемых для запоминания (хранения) наименьшей единицы данных (бит или байт).

Ячейки памяти имеют адрес (порядковый номер, число) по которому к ним могут обращаться команды процессора. Существует несколько различных систем адресации памяти.

Ячейки памяти, построенные на полупроводниковых технологиях, могут быть статическими (SRAM), то есть не требующими регулярного обновления, и динамическими (DRAM), требующими периодической перезаписи для сохранения данных. Как правило, при помощи статических ячеек организуются кэши, при помощи динамических — ОЗУ.

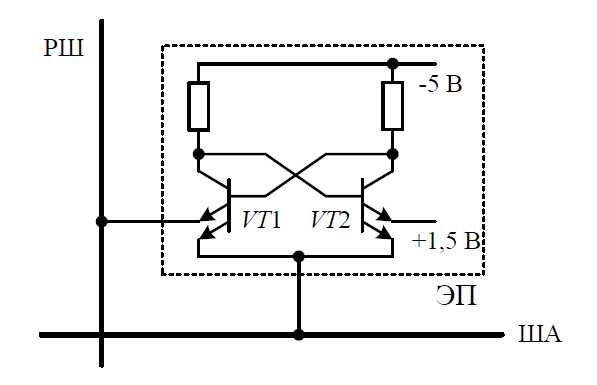

ЭП статического ЗУ, реализованного на асинхронном RS-триггере, построенного на основе логических элементов И–НЕ на многоэмиттерных транзисторах типа n-p-n.

(ША – шина адреса; РШ — разрядная шина)

Величина тока в РШ определяет состояние ЭП: наличие тока соответствует состоянию логической «1», а отсутствие – состоянию логического «0»

23. Структура памяти пэвм.

Оперативная память (ОЗУ) – реализуется, как правило, на модулях (микросхемах) динамической памяти. ОЗУ служит для хранения программы, исходных данных задачи, промежуточных и конечных результатов решения задачи.

Кроме оперативной, память включает также и постоянную (ПЗУ), из которой можно только считывать команды и данные, и некоторые виды специальной памяти (например видеопамять графического адаптера).

Все узлы не входящие в ядро называются периферийными. Они обеспечивают расширение возможностей, облегчают пользование ими. В состав периферийных (внешних) устройств могут входить следующие узлы.

Внешняя память (устройства хранения данных, например, дисковые) – память, имеющая относительно невысокое быстродействие, но по сравнению с ОЗУ существенно более высокую емкость.

Ключевым принципом построения памяти ПЭВМ является ее иерархическая организация (принцип, сформулированный еще Джоном фон Нейманом), которая предполагает использование в системе памяти компьютера запоминающих устройств (ЗУ) с различными характеристиками.

Запоминающие устройства (ЗУ) характеризуются рядом параметров, определяющих возможные области применения различных типов таких устройств. К основным параметрам, по которым производится наиболее общая оценка ЗУ, относятся их информационная емкость (E), время обращения (T) и стоимость (C).

Под информационной емкостью ЗУ понимают количество информации, измеряемое в байтах, килобайтах, мегабайтах или гигабайтах, которое может храниться в запоминающем устройстве.

studfiles.net

3.1. Назначение и структура центрального процессора : http://www.srinest.com/http://www.srinest.com/Организация ЭВМ и систем

Центральный процессор — основное устройство ЭВМ, которое наряду с обработкой данных выполняет функции управления системой: инициирование ввода-вывода, обработку системных событий, управление доступом к сновной памяти и т.п.

http://www.srinest.com/http://www.srinest.com/Организация центрального процессора (ЦП) определяется архитектурой и принципами работы ЭВМ (состав и форматы команд, представление чисел, способы адресации, общая организация машины и её основные элементы), а также технико-экономическими показателями.

Логическую структуру ЦП представляет ряд функциональных средств (рис. 3.1): средства обработки, средства управления системой и программой, локальная память, средства управления вводом-выводом и памятью, системные средства.

Средства обработки обеспечивают выполнение операций с фиксированной и плавающей точкой, операций с десятичными данными и полями переменной длины. Локальная память состоит из регистров общего назначения и с плавающей точкой, а также управляющих регистров. К средствам управления памятью относятся средства управления доступом к ОП и предвыборкой команд, буферная память, средства защиты памяти. Средства управления вводом-выводом обеспечивают приоритетный доступ программ через контроллеры (каналы) к периферийному оборудованию. К системным средствам относятся средства службы времени: часы астрономического времени, таймер, коммутатор и т.д.

Существует обязательный (стандартный) минимальный набор функциональных средств для каждого типа центрального процессора. Он включает в себя: регистры общего назначения, средства выполнения стандартного набора операций и средства управления вычислительным процессом. Конкретная реализация ЦП может различаться составом средств, способом их реализации, техническими параметрами.

Структурно все функциональные средства разбиваются на следующие

устройства (рис. 3.2): центральное устройство управления (ЦУУ), арифметико-логическое

устройство (АЛУ), устройство управления памятью (УУП), сверхоперативное

запоминающее устройство (СОЗУ), устройство предвыборки команд и данных (УП) и

интерфейс магистрали (ИМ).

Центральное устройство управления включает дешифратор команд, блок управления и блок прерываний. Дешифратор команд дешифрирует команды, которые поступают из блока предварительной выборки (очереди команд). Блок управления (БУ) формирует последовательности управляющих сигналов, которые поступают на все блоки процессора, обеспечивающие выполнение очередной команды и переход к следующей. Блок прерываний проводит анализ запросов на прерывания, формирует сигнал прерывания работы процессора и код (вектор) запроса с наивысшим приоритетом.

Арифметико-логическое устройство выполняет все арифметические и логические операции набора команд ЭВМ. В состав устройства входят традиционные арифметико-логические блоки, специализированные аппаратные средства (блок ускоренного умножения), буферные и рабочие регистры, иногда собственный блок управления. Во многих случаях выполнение операций с плавающей точкой осуществляется в отдельном блоке (процессоре), который имеет собственные регистры данных, управления и работает параллельно с центральным процессором.

Сверхоперативное ЗУ (регистровый файл) содержит регистры общего назначения (РОН), в которых хранятся данные и адреса.

Устройство управления памятью (диспетчер памяти) предназначено для сопряжения центрального процессора и подсистемы ввода-вывода с оперативной памятью. Оно состоит из блока сегментации и блока страничной адресации, осуществляющих двухступенчатое формирование физического адреса ячейки памяти: сначала в пределах сегмента, а затем в пределах страницы. Наличие блоков сегментации и страничной адресации, их одновременное функционирование обеспечивают максимальную гибкость проектируемой системы. Сегментация полезна для организации в памяти локальных модулей и является инструментом программиста, в то время как страницы нужны системному программисту для эффективного использования физической памяти системы.

Устройство предвыборки команд и данных включает блок предвыборки команд и внутреннюю кэш-память (кэш-память первого уровня). Первый осуществляет заполнение очереди команд, причем выборка из памяти производится в промежутках между магистральными циклами команд. Внутренняя кэш-память позволяет существенно повысить производительность процессора за счет буферизации в ней часто используемых команд и данных, сокращения числа обращений к оперативной памяти.

Интерфейс магистрали реализует протоколы обмена центрального процессора с

памятью, контроллерами (каналами) ввода-вывода, другими активными устройствами

системы. Обмен осуществляется с помощью шин данных, адреса и управления.

Состав линий управления, тактовая сетка, магистральные циклы обмена

существенно отличаются у различных типов процессоров.

В современных суперскалярных процессорах используется целый ряд параллельно функционирующих исполнительных устройств (от 2 до 6 устройств). В их состав могут входить:

— несколько целочисленных устройств;

— устройство плавающей точки;

— устройство выполнения переходов;

— устройство загрузки/записи.

Устройство выполнения переходов обрабатывает команды условных переходов. Если условия перехода доступны, то решение о направлений перехода принимается немедленно, в противном случае выполнение последующих команд продолжается по предположению (спекулятивно).

Пересылки данных между кэш-памятью данных, с одной стороны, и регистрами общего назначения и регистрами плавающей точки, с другой стороны, обрабатываются устройством загрузки/записи.

Центральный процессор — основное устройство ЭВМ, которое наряду с обработкой данных выполняет функции управления системой: инициирование ввода-вывода, обработку системных событий, управление доступом к сновной памяти и т.п.

http://www.srinest.com/http://www.srinest.com/Организация центрального процессора (ЦП) определяется архитектурой и принципами работы ЭВМ (состав и форматы команд, представление чисел, способы адресации, общая организация машины и её основные элементы), а также технико-экономическими показателями.

Логическую структуру ЦП представляет ряд функциональных средств (рис. 3.1): средства обработки, средства управления системой и программой, локальная память, средства управления вводом-выводом и памятью, системные средства.

Средства обработки обеспечивают выполнение операций с фиксированной и плавающей точкой, операций с десятичными данными и полями переменной длины. Локальная память состоит из регистров общего назначения и с плавающей точкой, а также управляющих регистров. К средствам управления памятью относятся средства управления доступом к ОП и предвыборкой команд, буферная память, средства защиты памяти. Средства управления вводом-выводом обеспечивают приоритетный доступ программ через контроллеры (каналы) к периферийному оборудованию. К системным средствам относятся средства службы времени: часы астрономического времени, таймер, коммутатор и т.д.

Существует обязательный (стандартный) минимальный набор функциональных средств для каждого типа центрального процессора. Он включает в себя: регистры общего назначения, средства выполнения стандартного набора операций и средства управления вычислительным процессом. Конкретная реализация ЦП может различаться составом средств, способом их реализации, техническими параметрами.

Структурно все функциональные средства разбиваются на следующие

устройства (рис. 3.2): центральное устройство управления (ЦУУ), арифметико-логическое

устройство (АЛУ), устройство управления памятью (УУП), сверхоперативное

запоминающее устройство (СОЗУ), устройство предвыборки команд и данных (УП) и

интерфейс магистрали (ИМ).

Центральное устройство управления включает дешифратор команд, блок управления и блок прерываний. Дешифратор команд дешифрирует команды, которые поступают из блока предварительной выборки (очереди команд). Блок управления (БУ) формирует последовательности управляющих сигналов, которые поступают на все блоки процессора, обеспечивающие выполнение очередной команды и переход к следующей. Блок прерываний проводит анализ запросов на прерывания, формирует сигнал прерывания работы процессора и код (вектор) запроса с наивысшим приоритетом.

Арифметико-логическое устройство выполняет все арифметические и логические операции набора команд ЭВМ. В состав устройства входят традиционные арифметико-логические блоки, специализированные аппаратные средства (блок ускоренного умножения), буферные и рабочие регистры, иногда собственный блок управления. Во многих случаях выполнение операций с плавающей точкой осуществляется в отдельном блоке (процессоре), который имеет собственные регистры данных, управления и работает параллельно с центральным процессором.

Сверхоперативное ЗУ (регистровый файл) содержит регистры общего назначения (РОН), в которых хранятся данные и адреса.

Устройство управления памятью (диспетчер памяти) предназначено для сопряжения центрального процессора и подсистемы ввода-вывода с оперативной памятью. Оно состоит из блока сегментации и блока страничной адресации, осуществляющих двухступенчатое формирование физического адреса ячейки памяти: сначала в пределах сегмента, а затем в пределах страницы. Наличие блоков сегментации и страничной адресации, их одновременное функционирование обеспечивают максимальную гибкость проектируемой системы. Сегментация полезна для организации в памяти локальных модулей и является инструментом программиста, в то время как страницы нужны системному программисту для эффективного использования физической памяти системы.

Устройство предвыборки команд и данных включает блок предвыборки команд и внутреннюю кэш-память (кэш-память первого уровня). Первый осуществляет заполнение очереди команд, причем выборка из памяти производится в промежутках между магистральными циклами команд. Внутренняя кэш-память позволяет существенно повысить производительность процессора за счет буферизации в ней часто используемых команд и данных, сокращения числа обращений к оперативной памяти.

Интерфейс магистрали реализует протоколы обмена центрального процессора с

памятью, контроллерами (каналами) ввода-вывода, другими активными устройствами

системы. Обмен осуществляется с помощью шин данных, адреса и управления.

Состав линий управления, тактовая сетка, магистральные циклы обмена

существенно отличаются у различных типов процессоров.

В современных суперскалярных процессорах используется целый ряд параллельно функционирующих исполнительных устройств (от 2 до 6 устройств). В их состав могут входить:

— несколько целочисленных устройств;

— устройство плавающей точки;

— устройство выполнения переходов;

— устройство загрузки/записи.

Устройство выполнения переходов обрабатывает команды условных переходов. Если условия перехода доступны, то решение о направлений перехода принимается немедленно, в противном случае выполнение последующих команд продолжается по предположению (спекулятивно).

Пересылки данных между кэш-памятью данных, с одной стороны, и регистрами общего назначения и регистрами плавающей точки, с другой стороны, обрабатываются устройством загрузки/записи.

www.srinest.com

8.2.2. Назначение и структура простейшего процессора.

Центральный процессор— это основной рабочий компонент компьютера, который выполняет арифметические и логические операции, управляет вычислительным процессом и координирует работу всех устройств компьютера.

Центральный процессор в общем случае содержит в себе:

арифметико-логическое устройство;

шины данных и шины адресов;

регистры;

счетчики команд;

кэш — очень быструю память малого объема,

математический сопроцессор чисел с плавающей точкой.

Современные процессоры выполняются в виде микропроцессоров. Физически микропроцессор представляет собой интегральную схему — тонкую пластинку кристаллического кремния прямоугольной формы площадью всего несколько квадратных миллиметров, на которой размещены схемы, реализующие все функции процессора. Кристаллическая пластинка обычно помещается в пластмассовый или керамический плоский корпус и соединяется золотыми проводками с металлическими штырьками, чтобы его можно было присоединить к системной плате компьютера.

Основные характеристики процессора :

Производительность — основная характеристика, показывающая скорость выполнения компьютером операций обработки информации. Она в свою очередь зависит от следующих характеристик:

Тактовая частота — определяет число тактов работы процессора в секунду

Разрядность — определяет размер минимальной порции информации, называемой машинным словом

Адресное пространство — разрядность адресной шины, то есть максимальный объём оперативной памяти, которая может быть установлена на компьютере

8.2.3. Принцип действия процессора.

Процессор является главным элементом ЭВМ. Он прямо или косвенно управляет всеми устройствами и процессами, происходящими в ЭВМ.

В конструкции современных процессоров четко просматривается тенденция постоянного увеличения тактовой частоты. Это естественно: чем больше операций выполняет процессор, тем выше его производительность. Предельная тактовая частота во многом определяется существующей технологией производства микросхем (наименьшими достижимыми размерами элементов, которые определяют минимальное время передачи сигналов).

Кроме повышения тактовой частоты, увеличение производительности процессоров достигается разработчиками менее очевидными приемами, связанными с изобретением новых архитектур и алгоритмов обработки информации. Некоторые из них рассмотрим на примере процессора Pentium (Р5) и последующих моделей.

Перечислим основные особенности процессора Pentium:

конвейерная обработка информации;

суперскалярная архитектура;

наличие раздельных кэш-памятей для команд и данных;

наличие блока предсказания адреса перехода;

динамическое исполнение программы;

наличие блока вычислений с плавающей точкой;

поддержка многопроцессорного режима работы;

наличие средства обнаружения ошибок.

Термин «суперскалярная архитектура» означает, что процессор содержит более одного вычислительного блока. Эти вычислительные блоки чаще называют конвейерами. Заметим, что первая суперскалярная архитектура была реализована в отечественной ЭВМ «Эльбрус-1» (1978 г.).

Наличие в процессоре двух конвейеров позволяет ему одновременно выполнять (завершать) две команды (инструкции).

Каждый конвейер разделяет процесс выполнения команды на несколько этапов (например, пять):

выборка (считывание) команды из ОЗУ или кэш-памяти;

декодирование (дешифрация) команды, т. е. определение кода выполняемой операции;

выполнение команды;

обращение к памяти;

запоминание полученных результатов в памяти.

Для реализации каждого из перечисленных этапов (каждой операции) служит отдельное устройство— ступень. Таким образом, в каждом конвейере процессора Pentium имеется пять ступеней.

При конвейерной обработке на выполнение каждого этапа отводится один такт синхронизирующей (тактовой) частоты. В каждом новом такте заканчивается выполнение одной команды и начинается выполнение новой команды. Такое выполнение команд называют поточной обработкой.

Образно ее можно сравнить с производственным конвейером (потоком), где на каждом участке с разными изделиями выполняют всегда одну и ту же операцию. При этом, когда готовое изделие сходит с конвейера, на него заходит новое, а остальные изделия в это время находятся на разных стадиях готовности. Переход изготавливаемых изделий с участка на участок должен происходить синхронно, по специальным сигналам (в процессоре это такты, формируемые тактовым генератором).

Общее время выполнения одной команды в конвейере с пятью ступенями будет составлять пять периодов тактовой частоты. В каждом такте конвейер будет одновременно обрабатывать (выполнять) пять различных команд. В результате за пять тактов будет выполнено пять команд. Таким образом, конвейеризация увеличивает производительность процессора, но она не сокращает время выполнения отдельной команды. Выигрыш получается за счет того, что обрабатывается сразу несколько команд.

В действительности конвейеризация даже увеличивает время выполнения каждой отдельной команды из-за появления дополнительных расходов, связанных с организацией работы конвейера. При этом тактовая частота ограничивается быстродействием работы самой медленной ступени конвейера.

В качестве примера рассмотрим процесс выполнения команды, у которой длительности выполнения этапов составляют 60, 30, 40, 50 и 20 нс. Примем дополнительные расходы на организацию конвейерной обработки равными 5 нс.

Если бы не было конвейеризации, то на выполнение одной команды потребовалось

60 + 30 + 40 + 50 + 20 = 200 нс.

Если же используется конвейерная организация, то длительность такта должна быть равна длительности самого медленного этапа обработки с добавлением «накладных» расходов, т.е. 60 + 5 = 65 нс. Таким образом, полученное в результате конвейеризации сокращение времени выполнения команды составит 200/65»3,1 раза.

Заметим, что время выполнения конвейером одной команды составляет 5 × 65 = 325 нс. Эта величина существенно больше 200 нс — времени выполнения команды без конвейеризации. Но одновременное выполнение сразу пяти команд дает среднее время завершения одной команды 65 нс.

Процессор Pentium имеет две кэш-памяти первого уровня (они расположены внутри процессора). Как известно, кэширование увеличивает производительность процессора за счет уменьшения числа случаев ожидания поступления информации из медленной оперативной памяти. Нужные данные и команды берутся процессором из быстрой кэш-памяти (буфера), куда они заносятся заранее.

Наличие одной кэш-памяти в предыдущих конструкциях процессоров приводило к возникновению структурных конфликтов. Две команды, выполнявшиеся конвейером, порой одновременно пытались считать информацию из единственной кэш-памяти. Выполнение раздельного кэширования (буферизации) для команд и данных исключает такие конфликты, давая возможность обеим командам выполняться одновременно.

Развитие вычислительной техники идет непрерывно. Постоянно конструкторы ищут новые пути совершенствования своих изделий. Наиболее ценным ресурсом процессоров является их производительность. По этой причине изобретаются разнообразные приемы повышения производительности процессоров.

Одним из таких приемов является экономия времени за счет предсказания возможных путей выполнения разветвляющегося алгоритма. Это осуществляется с помощью блока предсказания адреса будущего перехода. Идея его работы похожа на идею работы кэш-памяти.

Как известно, существуют линейные, циклические и разветвляющиеся вычислительные процессы. В линейных алгоритмах команды выполняются в порядке их записи в оперативной памяти: последовательно одна за другой. Для таких алгоритмов введенный в процессор блок предсказания адреса перехода не может дать выигрыша.

В разветвляющихся алгоритмах выбор команды определяется результатами проверки условий ветвлений. Если ждать окончания вычислительного процесса в точке ветвления и затем выбирать из ОЗУ нужную команду, то неизбежно появятся потери времени из-за непроизводительного простоя процессора (считывание команды из ОЗУ идет медленно).

Блок предсказания адреса перехода работает на опережение и пытается заблаговременно предсказать адрес перехода, чтобы заранее перенести нужную команду из медленной оперативной памяти в специальный быстрый буфер перехода BTB (Branch Target Buffer).

Когда буфер ВТВ содержит правильное предсказание, переход происходит без задержки. Это напоминает работу кэш-памяти, у которой также бывают промахи. Из-за промахов операнды приходится считывать не из кэш-памяти, а из медленной ОП. Из-за этого происходит потеря времени.

Реализацию идеи предсказания адреса перехода осуществляют в процессоре два независимых буфера предварительной выборки. Они работают совместно с буфером предсказания переходов, причем один из буферов выбирает команды последовательно, а второй — согласно предсказаниям ВТВ.

Процессор Pentium имеет два пятиступенчатых конвейера для выполнения операций в формате с фиксированной точкой. Кроме того, в процессоре имеется конвейер с восьмью ступенями для вычислений в формате с плавающей точкой. Такие вычисления требуются при выполнении математических расчетов, а также для быстрой обработки динамических трехмерных цветных изображений.

Развитие архитектуры процессоров идет по пути постоянного увеличения объема кэш-памяти первого и второго уровней. Исключением стал процессор Pentium 4, у которого объем кэш-памяти неожиданно снизился по сравнению с Pentium III.

Для повышения производительности в новых конструкциях процессоров создают две системные шины, работающие с разными тактовыми частотами. Быстрая шина используется для работы с кэш-памятью второго уровня, а медленная — для традиционного обмена информацией с другими устройствами, например ОЗУ. Наличие двух шин исключает конфликты при обмене информацией процессора с основной памятью и кэш-памятью второго уровня, находящейся за пределами кристалла процессора.

Следующие за Pentium процессоры содержат большое число ступеней в конвейере. Это уменьшает время выполнения каждой операции в отдельной ступени, а значит, позволяет поднять тактовую частоту процессора.

В процессоре Pentium Pro (P6) применен новый подход к порядку выполнения команд, последовательно расположенных в ОЗУ.

Новый подход заключается в выполнении команд в произвольном порядке по мере их готовности (независимо от порядка расположения в ОЗУ). Однако конечный результат формируется всегда в соответствии с исходным порядком команд в программе. Такой порядок выполнения команд называется динамическим или опережающим.

Рассмотрим в качестве примера следующий фрагмент учебной программы, записанной на некотором (вымышленном) машинно-ориентированном языке.

r1 ¬mem[r4] Команда 1

r3 ¬r1 + r2 Команда 2

r5 ¬r5 + 1 Команда 3

r6 ¬r6 – r7 Команда 4

Символами r1…r7 обозначены регистры общего назначения (РОН), которые входят в блок регистров процессора.

Символом mem[r4]обозначена ячейка памяти ОЗУ.

Прокомментируем записанную программу.

Команда 1: записать в РОН r1 содержимое ячейки памяти ОЗУ, адрес которой указан в РОН r4.

Команда 2: записать в РОН r3 результат сложения содержимого регистров r1 и r2.

Команда 3: прибавить к содержимому регистра r5 единицу.

Команда 4: уменьшить содержимое РОН r6 на содержимое регистра r7.

Предположим, что при выполнении команды 1 (загрузка операнда из памяти в регистр общего назначения r1) оказалось, что содержимое ячейки памяти mem [r4] отсутствует в кэш-памяти процессора (произошел промах, нужный операнд не был заранее доставлен в буфер из ОЗУ).

При традиционном подходе процессор перейдет к выполнению команд 2, 3, 4 только после того, как данные из ячейки mem[r4] основной памяти поступят в процессор (точнее, в регистр r1). Так как считывание будет происходить из медленно работающей оперативной памяти, этот процесс займет достаточно много времени (по меркам процессора). Все время ожидания этого события процессор будет простаивать, не выполняя полезной работы.

В приведенном примере процессор не может выполнить команду 2 до завершения команды 1, так как команда 2 использует результаты выполнения команды 1. В то же время процессор мог бы заранее выполнить команды 3 и 4, которые не зависят от результата выполнения команд 1 и 2.

В подобных случаях процессор Р6 работает иначе.

Процессор Р6 не ждет окончания выполнения команд 1 и 2, а сразу переходит к внеочередному выполнению команд 3 и 4. Результаты опережающего выполнения команд 3 и 4 сохраняются и извлекаются позднее, после выполнения команд 1 и 2.Таким образом, процессор Р6 выполняет команды в соответствии с их готовностью к выполнению, вне зависимости от их первоначального расположения в программе.

Производительность, безусловно, важный показатель работы ЭВМ. Однако не менее важно, чтобы быстрые вычисления происходили при малом числе ошибок.

В процессоре имеется устройство самотестирования, которое автоматически проверяет работоспособность большинства элементов процессора.

Кроме того, выявление сбоев, произошедших внутри процессора, осуществляется с помощью специального формата данных. К каждому операнду добавляется бит четности, в результате чего все циркулирующие внутри процессора числа становятся четными. Появление нечетного числа сигнализирует о случившемся сбое. Наличие нечетного числа — это как бы появление фальшивой банкноты без водяных знаков.

Единицами измерения быстродействия процессоров (и ЭВМ) могут служить:

МИПС (MIPS— Mega Instruction Per Second)— миллион команд (инструкций) над числами с фиксированной точкой за секунду;

МФЛОПС (MFLOPS— Mega Floating Operation Per Second)— миллион операций над числами с плавающей точкой за секунду;

ГФЛОПС (GFLOPS— Giga Floating Operation Per Second)— миллиард операций над числами с плавающей точкой за секунду.

Имеются сообщения о самом быстром в мире компьютере ASCI White (корпорация IBM), быстродействие которого достигает 12,3 ТФЛОПС (триллиона операций).

studfiles.net

6.1 Типовая структура процессора

Тема.6 Процессоры

Процессором называется устройство, непосредственно осуществляющее процесс обработки данных и программное управление этим процессом. Процессор дешифрует и выполняет команды программы, организует обращение к ОП, в нужных случаях инициирует работу ПУ, воспринимает и обрабатывает запросы, поступающие от устройств машины и из внешней среды («запросы прерывания»).

Процессор занимает центральное место в структуре ЭВМ, т.к. он осуществляет управление взаимодействием всех устройств, входящих в состав ЭВМ.

Выполнение команды (машинные операции) разделено на более мелкие операции — микрооперации (микрокоманды), выполняющие определенные элементарные действия. Конкретный состав микроопераций определяется системой команд и логической структурой данной ЭВМ. Последовательность микроопераций (машинных команд), реализующих данную операцию (команду), образует микропрограмму операции.

Для определения временных соотношений между различными этапами операций используется понятие машинного такта. Машинный такт определяет интервал времени, в течение которого выполняется одна или одновременно несколько микроопераций. Границы такта задаются синхросигналами, вырабатываемых генератором синхросигналов. Иерархия этапов выполнения программ в процессоре:

Программакомандамикрооперации

Упрощенная схема процессора представлена на рис.6.1. Здесь изображены только его составные части: АЛУ, управляющее устройство (управляющий автомат), блок управляющих регистров БУР, блок регистровой памяти (местная память) и блок связи с ОП и др., в том числе и внешним оборудованием.

В состав процессора могут входить также и некоторые другие блоки, участвующие в организации вычислительного процесса (блок прерывания, блок защиты памяти, блок контроля правильности работы и диагностики процессора и др.)

ОП выполняется в виде отдельного устройства, которое в небольших ЭВМ может конструктивно объединяться с процессором и использовать частично его оборудование.

Основные части МП:

Арифметико-логическое устройство АЛУ процессора выполняет арифметические и логические операции над данными. В общем случае АЛУ выполняет логические преобразования над отдельными группами бит, байтами и их последовательностями, арифметические операции над числами с фиксированной и плавающей запятой, над десятичными числами, обработка алфавитно-цифровых слов переменной длинны и др. В процессоре может быть одно универсальное АЛУ для выполнения основных арифметических и логических преобразований или несколько специализированных для отдельных видов операций, например, векторных операций, с плавающей запятой, десятичных операций. В последнем случае увеличивается количество оборудования процессора, но повышается его быстродействие за счет специализации и упрощения схем выполнения отдельных операций.

Управляющее устройство УУ – комплекс средств автоматического управления процессом передачи и обработки информации. УУ принимает и расшифровывает команды, формирует адреса команд и операндов, формирует последовательность управляющих сигналов и обеспечивает координацию работы функциональных узлов посредством выдачи управляющих и синхронизирующих сигналов.

УУ по способу построения делятся на УУ с жесткой логикой и УУ с микропрограммным управлением.

Блок управляющих регистров предназначен для временного хранения управляющей информации. Он содержит регистры и счетчики, участвующие в управлении вычислительным процессом: регистры, хранящие информацию о состоянии процессора, регистр-счетчик адреса команд – счетчик команд, счетчики тактов, регистр запросов и т.д.

Блок регистровой памяти (местная память) небольшой емкости, но более высокого, чем ОП, быстродействия, предназначен для повышения быстродействия и логических возможностей процессора. Регистры этого блока используются для хранения операндов, в качестве аккумуляторов (регистров результата операций), базовых и индексных регистров, указателя стека. В некоторых процессорах базовые и индексные регистры входят в состав управляющих регистров.

Блок связи (интерфейс процессора) организует обмен информацией процессора с ОП и защиту участков ОП от недозволенных данной программе обращений, а также связь процессора с периферийными устройствами ПУ и внешним по отношению к ЭВМ оборудованием (др. ЭВМ и т.д.).

Блок рег.памяти

АЛУ

УУ

БУР

Блок связи с ОП

ВУ

Команды операнды (из ОП)

Результаты операций в

(в ОП)

……

ЗПр

Рисунок 6.1

6. Блок контроля и диагностики (на рисунке не показан) служит для обнаружения сбоев и отказов в аппаратуре процессора, восстановления работы программы после сбоев и поиска места неисправности при отказах.

studfiles.net

6. Структура центрального процессора.

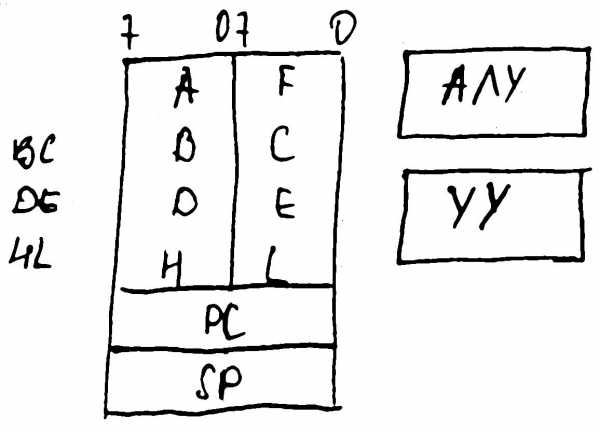

Структуру центрального процессора можно представить следующим образом:

Основными составными частями центрального процессора являются: блок регистров, АЛУ – арифметическо-логическое устройство и устройство управления (УУ).

Регистр A – аккумулятор.

6 регистров общего назначения B, C, D, E, H, L, могут объединяться в пары.

Регистр F – регистр флагов, отдельные разряды этого регистра принято называть флагами, CY – один из флагов.

Два шестнадцатиразрядных регистра PC – программный счетчик. SP – регистр указателя стека. PC – такой регистр, в котором в конце выполнения очередной команды устанавливается адрес следующей выполняемой команды.

АЛУ предназначено для выполнения арифметических и логических операций с двоичным кодом.

УУ предназначено для управления последовательного выполнения команд ЦП.

7. Структура команды и способы адресации.

Первый байт любой команды называется кодом операции. Второй и третий байты команды назначение зависит от способа адресации операндов в команде.

Операнд – те данные, с которыми оперирует команда. Бывают исходными и результирующими.

Основные способы адресации операндов.

Регистровый способ – операнд находится в одном из регистров ЦП.

Прямой способ. Адрес операнда находится в команде, во втором байте или во втором и третьем байтах.

Непосредственный способ. Операнд находится в команде.

Косвенный способ. Операнд находится в памяти, а его адрес в регистровой паре (HL).

8Система команд. Команды пересылки.

Все возможные команды, которые может выполнить ЦП, называют системой команд это ЦП. Эту систему команда можно разделить на группы:

Команды пересылки.

Команды логических операций.

Команды арифметических операций.

Команды передачи управления.

Специальные команды.

Команды пересылки.

MOV R1, R2 – команда пересылки (MOV A, B – мнемокод). 2 операнда R1 и R2. В качестве R1 и R2 в данной команде могут выступать один из регистров общего назначения. R1 R2.

Данная команда имеет регистровый способ адресации, имеет размер 1 байт, и для ее выполнения нужно одно обращение к памяти (чтение)

Для записи двоичного кода, в шестандацатиричный, код разбивают по четыре разряда (начиная с младшего), каждые четыре разряда записываются цифрой.

Запись команд в мнемокодах производится в программах, написанных на языке ассемблера. Ассемблер – язык низкого уровня. Он специфичен для каждого типа микропроцессора. Языки высокого уровня не связываются с конкретным типом микропроцессора.

LDA ADDR

Команда адрес в команде

Команда трех байтная. Первый байт – код операции, второй байт и третий – адрес памяти, который находится в команде. Команда пересылает содержимое содержимое ячейки памяти с адресом, записанным во втором и третьем байте команды в аккумулятор.

A ADDR. В данной команде имеется два способа адресации операндов. Исходный операнд, находящийся в памяти адресуется прямым способом адресации. Результирующий передается регистровым способом адресации. 4 раза обращается к памяти.

STA ADDR (ADDR A)

MOV R, M (R(HL)) – в регистр общего назначения переносится содержимое регистра HL.

MOV A, M. В этой команде используется два способа передачи. Исходный операнд, находится в памяти, адресуется косвенным способом. Его адрес перед выполнением команды должен быть помещен в регистровую пару HL. Результирующий операнд находится в аккумуляторе (A). и адресуется регистровым способом. Команда имеет размер 1 байт и для ее выполнения требуется 2 операнда.

MOV M, R – обратная команда.

IN PORT (ввода) A (PORT)

OUT PORT (вывод) (PORT) A.

Где PORT – адрес порта. Команды двухбайтные. Для выполнения требуется 2 регистра.

PUSH RP. Обращение к стековой области памяти. RP – регистровая пара. Содержимое регистровой пары перемещается в стековую область памяти.

SP – регистр указателя стека. В состав регистров ЦП входит SP, шестнадатиразрядный. Содержимое этого регистра является адресом последней заполненной ячейки стековой области памяти. Работа стековой области памяти осуществляется по принципу: «последний пришел, первый вышел».

В данном микропроцессоре стековая область памяти заполняется в сторону уменьшения адресов. При выполнении 1 команды заполняются две ячейки стековой области памяти.

DOP RP – извлечение информации из стековой области памяти. Однобайтовая команда. Три обращения к памяти.

studfiles.net